半導体製造の新たな可能性が、日本から生まれようとしている。キヤノンが約20年かけて実用化したナノインプリント技術は、光ではなく「型」で回路を刻む。ASMLのEUV装置が1億5000万ドルを超える中、その10分の1のコストで5nmプロセスに挑む。12月に開催されるSEMICON Japan 2025で、キヤノングループが示すのは、生成AI時代の半導体製造における異なる道筋だ。技術革新とは、必ずしも最先端を追うことだけではない。

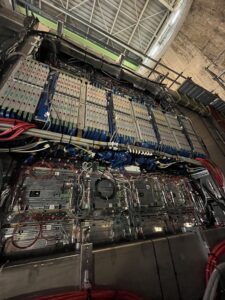

キヤノン、キヤノンアネルバ、キヤノンマシナリーの3社は、2025年12月17日から19日まで東京ビッグサイトで開催される半導体産業の国際展示会「SEMICON Japan 2025」に出展する。前工程向けにナノインプリント技術を用いた半導体製造装置「FPA-1200NZ2C」、後工程向け露光装置「FPA-5520iV LF2オプション」、複合現実システム「MREAL」を展示する。キヤノンアネルバは「iFデザインアワード2025」プロダクト分野で金賞を受賞した成膜装置シリーズ「Adastra」のモックアップ、原子拡散接合装置「BC7300」を紹介する。キヤノンマシナリーは12インチウエハー対応ダイボンダー「BESTEM-D610」の実機デモを行う。キヤノンは製品ライフサイクル全体でのCO₂排出量を2050年までにネットゼロとする目標を掲げ、UV-LED露光オプションなど環境配慮の取り組みを紹介する。

From: ![]() キヤノンが「SEMICON Japan 2025」に出展 半導体製造の多様化に対応する装置や環境配慮の取り組みを紹介

キヤノンが「SEMICON Japan 2025」に出展 半導体製造の多様化に対応する装置や環境配慮の取り組みを紹介

【編集部解説】

キヤノングループが12月のSEMICON Japanで披露する半導体製造装置群は、単なる製品ラインアップの展示以上の意味を持ちます。これは生成AI需要が引き起こす半導体製造の構造変化に、日本企業がどう応えようとしているかを示す重要なシグナルです。

半導体産業は今、前例のない転換点を迎えています。Bloomberg Intelligenceの分析によれば、先端パッケージング市場は2033年までに805億ドル規模へと8倍に成長し、年平均成長率26%という驚異的なペースで拡大すると予測されています。この背景にあるのは、データセンターから始まったAIチップ需要が、PC、スマートフォン、自動車へと広がる大きな波です。

キヤノンが注力するナノインプリントリソグラフィ(NIL)技術は、この変化に対する戦略的な回答といえます。従来の露光装置が光を使ってパターンを転写するのに対し、NILは型を直接押し当てて回路パターンを形成する、まったく異なるアプローチです。ASMLのEUV装置が1億5000万ドル以上するのに対し、NILは「1桁安い」コストで5nmプロセスに対応でき、電力消費も最大90%削減できるとキヤノンは主張しています。

2025年7月にキヤノンは宇都宮に21年ぶりとなる新工場を開設し、500億円を投じて生産能力を50%増強しました。同社は今後3〜5年で年間10〜20台のNIL装置販売を目指しており、2024年9月にはIntelやSamsungが参画するテキサス・エレクトロニクス研究所へ初納入を果たしています。これは技術の実用化に向けた重要な一歩です。

ただし、NIL技術にはまだ課題も残っています。業界専門家は、量産に必要な歩留まり率を90%近くまで高める必要があると指摘しています。また、既存のEUV向けに最適化された製造プロセスへの統合も、容易ではありません。キヤノン自身も「量産に求められるレベルに到達するには、まだ課題に直面している」と認めています。

一方、キヤノンアネルバが展示するAdastraシリーズは、2025年3月にiFデザインアワードで最高位の金賞を受賞した成膜装置です。この装置の最大の特徴は省スペース設計にあります。半導体工場では床面積がそのままコストに直結するため、同じ面積により多くの装置を配置できることは、製造効率の大幅な向上を意味します。

後工程向けの装置群も見逃せません。先端パッケージング技術は、もはや半導体性能向上の鍵を握る領域となっています。IDCによれば、TSMCのCoWoS生産能力は2024年の33万ウエハーから2025年には66万ウエハーへと倍増する計画で、これはNvidia、AMD、Broadcomといった顧客からの旺盛な需要に応えるためです。

キヤノンマシナリーのダイボンダー「BESTEM-D610」は、こうした先端パッケージングの需要増に対応する装置です。12インチウエハーへの対応は、大口径化が進む業界トレンドに沿ったものといえます。

環境配慮の取り組みも重要なポイントです。キヤノンは2050年までに製品ライフサイクル全体でのCO₂排出量をネットゼロにする目標を掲げています。UV-LED露光オプションは、従来の水銀ランプを使わないため、脱水銀と省エネルギー化を同時に実現します。装置の長寿命化技術も、資源循環の観点から注目に値します。

SEMICON Japan 2025には1,200以上の企業が出展し、併催イベントとして先端パッケージング・チップレットサミット(APCS)も開催されます。AI半導体、量子コンピューティング、フォトニクス・エレクトロニクス融合など、次世代技術が一堂に会するこのイベントで、キヤノングループがどのような反響を得るか注目されます。

長期的な視点で見れば、半導体製造装置市場における競争構造そのものが変わりつつあります。ASMLが圧倒的なシェアを持つEUV市場に対し、キヤノンは異なる技術パスで挑戦しています。もしNILが量産技術として確立されれば、先端半導体製造のコスト構造が大きく変わり、新たなプレイヤーの参入を促す可能性もあります。

日本の半導体装置産業は2024年に輸出額4.5兆円という記録を達成しました。キヤノングループの挑戦は、この勢いをさらに加速させる原動力となるかもしれません。ナノインプリント技術が本当にゲームチェンジャーとなるのか、それとも特定用途に限られるニッチ技術にとどまるのか。SEMICON Japan 2025での反応が、その答えの一端を示すことになるでしょう。

【用語解説】

ナノインプリントリソグラフィ(NIL)

型を直接押し当てて回路パターンを形成する半導体製造技術。従来の光リソグラフィと異なり、光学系を必要としないため、低コストで微細なパターン形成が可能となる。キヤノンは約20年開発を続け、2023年に商用化を実現した。

EUV(極端紫外線)リソグラフィ

波長13.5nmの極端紫外線を使用する最先端の半導体露光技術。オランダのASMLが独占的に製造しており、1台1億5000万ドル以上する高額装置だが、5nm以下の先端プロセスに不可欠とされている。

先端パッケージング

複数のチップを一つのパッケージ内に統合する技術の総称。2.5D、3D積層、チップレット技術などが含まれる。AIやHPC向けチップの性能向上に不可欠な技術として急速に発展している。

CoWoS(Chip on Wafer on Substrate)

TSMCが開発した2.5D/3D先端パッケージング技術。プロセッサとHBM(高帯域メモリ)を同一パッケージに実装することで、データ転送速度を大幅に向上させる。

成膜装置

半導体製造において、ウエハー表面に薄膜を形成する装置。金属膜、絶縁膜、誘電体膜など、用途に応じた材料を堆積させる工程で使用される。

原子拡散接合

原子レベルでウエハー同士を接合する技術。3D積層パッケージングにおいて、チップ間の接続密度を高め、信号遅延を最小化するために用いられる。

ダイボンダー

半導体チップ(ダイ)を基板やパッケージに実装する装置。後工程における重要な工程の一つで、高精度な位置決めと接着が求められる。

MREAL(エムリアル)

キヤノンが開発した複合現実(MR)システム。実世界にCGを重ねて表示することで、設計検証や製造プロセスの可視化などに活用される。

HBM(High Bandwidth Memory)

高帯域幅メモリの略称。従来のDDRメモリと比較して、データ転送速度が飛躍的に高く、消費電力が低い。AI・HPC向けチップに広く採用されている。

チップレット

大型の単一チップではなく、機能ごとに分割した小型チップ(チップレット)を組み合わせてシステムを構成する設計手法。製造コスト削減と歩留まり向上が期待できる。

【参考リンク】

キヤノン株式会社(外部)

カメラ・プリンターで知られる総合イメージング企業。近年は半導体製造装置事業を強化している。

キヤノンアネルバ株式会社(外部)

キヤノングループの半導体製造装置メーカー。真空薄膜形成装置やエッチング装置を手がける。

キヤノンマシナリー株式会社(外部)

半導体製造装置、特に後工程装置の製造を担うキヤノングループ企業。

SEMICON Japan 2025公式サイト(外部)

日本最大の半導体産業展示会。毎年12月に東京ビッグサイトで開催される。

SEMI(国際半導体製造装置材料協会)(外部)

世界の半導体・エレクトロニクス製造サプライチェーンを代表する国際業界団体。

TSMC(台湾積体電路製造)(外部)

世界最大の半導体受託製造企業。CoWoSなど先端パッケージング技術でも業界をリードする。

iF International Forum Design(外部)

1953年設立のドイツのデザイン賞主催団体。iFデザインアワードは世界三大デザイン賞の一つ。

【参考記事】

Canon bets on nanoimprint: new Japan fab targets advanced chipmaking(外部)

キヤノンの宇都宮新工場について詳述。500億円投資、2027年に年間300システム以上の生産能力を目指す。

Canon Delivers Nanoimprint Lithography to Compete With EUV – IEEE Spectrum(外部)

ナノインプリント技術の詳細な技術解説。14nmの回路パターン形成が可能でEUVより低コストと報じる。

Canon delivers first nanoimprint lithography tool to US institute | Tom’s Hardware(外部)

2024年9月、テキサス・エレクトロニクス研究所へのNIL装置初納入を報道。Intel、Samsung参画の実証実験。

Advanced Semiconductor Packaging Market Could Reach $80 Billion by 2033 | Bloomberg(外部)

先端パッケージング市場が2033年までに805億ドル規模へ8倍成長との予測。年平均成長率26%。

Canon recognized with iF Design Award for 31st consecutive year | Canon Global(外部)

2025年3月、キヤノンアネルバのAdastraシリーズがiFデザインアワード2025で金賞受賞を発表。

IDC: Global Semiconductor Market to Grow by 15% in 2025, Driven by AI(外部)

2025年の半導体市場は15%以上成長と予測。TSMCのCoWoS生産能力は2025年に66万ウエハーへ倍増計画。

SEMICON Japan 2025 to Spotlight Sustainability in AI and Semiconductor Innovation | SEMI(外部)

SEMICON Japan 2025の開催概要。1,200以上の出展者、併催イベントAPCS、ADISの詳細を紹介。

【編集部後記】

キヤノンのナノインプリント技術は、半導体製造における「常識」を書き換えようとしています。光ではなく型で回路を刻むというアプローチは、一見すると後戻りのようにも感じられますが、むしろ本質的な問いを投げかけています。より高性能なチップを作るために、私たちは本当に何十億円もする装置が必要なのでしょうか。SEMICON Japanでキヤノンが披露する技術群は、日本の半導体産業復活への一つの道筋を示しています。皆さんはこの挑戦をどう見ますか。技術革新とは、必ずしも最先端を追うことだけではないのかもしれません。むしろ、異なる視点から問題を捉え直すことにこそ、真のブレークスルーが潜んでいるのではないでしょうか。